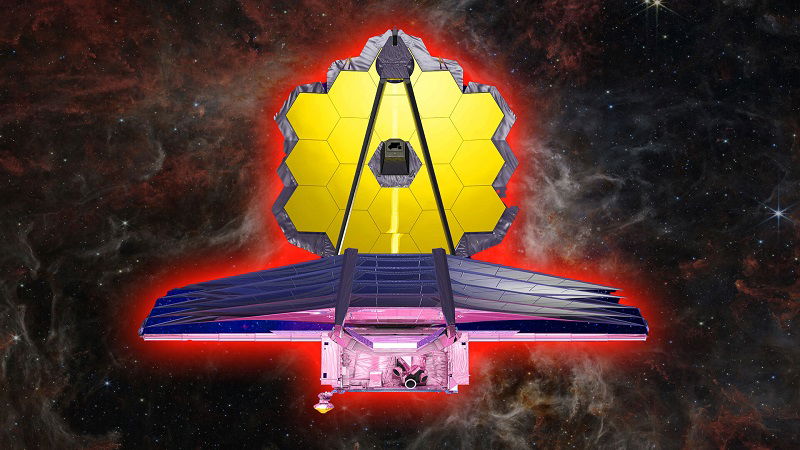

Broadcom Inc. today detailed a new chip packaging technology, XDSiP, that makes it possible to create processors by stacking multiple silicon dies atop another.

XDSiP is short for eXtreme Dimension System in Package. Broadcom is positioning it as a way to create more powerful data center chips. One customer, Fujitsu Ltd., will use the technology as the basis of an upcoming server processor with 288 cores.

Under the hood, XDSiP is based on an emerging chip manufacturing approach known as 3.5D packaging.

Many modern processors include multiple silicon dies that each focus on a different task. One might be optimized to run artificial intelligence models, while another may be geared towards general-purpose calculations. Often, there’s also a die dedicated to auxiliary tasks such as moving data in and out of the chip.

One way to link together the dies that make up a processor is to place them side-by-side on a base layer known as an interposer. This approach is called 2.5D chip packaging. Broadcom’s XDSiP technology makes it possible to create a processor in which dies are placed not only next to each other but also one atop another, which boosts the transistor count.

Broadcom links together the vertically stacked dies with a technology called hybrid copper bonding. It’s made through a complex multistep process that researchers are still in the process of refining.

In the first step of the workflow, copper structures are added to the top layer of two dies. Then, one of the dies is placed atop the other such that their respective copper structures directly face one another. Lastly, the copper structures are melted into a single interconnect that allows data and electricity to move between the dies.

One of the technology’s advantages over earlier approaches is that it allows data to move more quickly between a processor’s components. According to Broadcom, XDSiP provides seven times the signal density of an earlier packaging type called B2F. Additionally, it has better mechanical strength, which reduces the risk that applying pressure to the chip will cause malfunctions.

Processors made with 2.5D technology usually contain up to 2,500 square millimeters of silicon. According to Broadcom, its XDSiP technology provides the ability to add more than 6,000 square millimeters. The result is an increase in processing speeds.

“Broadcom’s 3.5D platform enables chip designers to pair the right fabrication processes for each component while shrinking the interposer and package size, leading to significant improvements in performance, efficiency and cost,” said Frank Ostojic, senior vice president and general manager of Broadcom’s ASIC Products Division.

The company detailed that more than five 3.5D products are currently in development for customers. Broadcom’s lead product includes four compute dies, one die dedicated to data input and output operations and six HBM modules. HBM is a type of high-speed memory widely used in AI chips.

Fujitsu, one of the customers that has adopted the technology, is using it as the basis of an upcoming server processor called Monaka. It will feature 288 Arm cores made using a two-nanometer process and cache modules based on five-nanometer technology. The cores will sit atop the cache modules, which will in turn be placed on an interposer.

Broadcom expects production shipments of XDSiP-based processors to begin in February 2026. Fujitsu plans to launch its Monaka chip in 2027.

Photo: Broadcom

Your vote of support is important to us and it helps us keep the content FREE.

One click below supports our mission to provide free, deep, and relevant content.

Join our community on YouTube

Join the community that includes more than 15,000 #CubeAlumni experts, including Amazon.com CEO Andy Jassy, Dell Technologies founder and CEO Michael Dell, Intel CEO Pat Gelsinger, and many more luminaries and experts.

THANK YOU

Leave a Comment