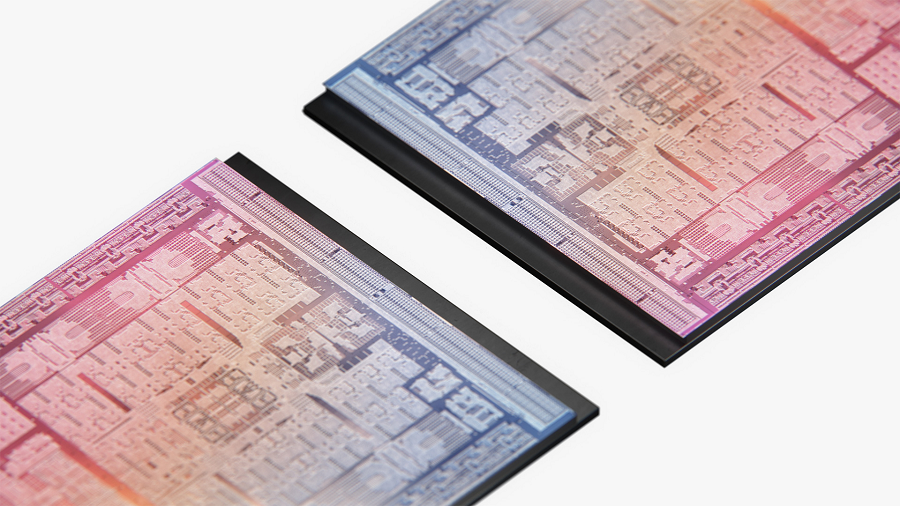

Apple Inc.’s upcoming M5 line of Mac chips will be made using Taiwan Semiconductor Manufacturing Co.’s three-nanometer N3P process, 9to5Mac reported today.

The publication attributed the information to Apple analyst Ming-Chi Kuo, who has a track record of successfully predicting product launches from the company. It’s believed some of the upcoming M5 chips will also use TSMC’s 2.5D packaging technology.

Apple’s M-series Mac chips each include a central processing unit, a graphics processing unit and an artificial intelligence accelerator. The latest M4 is available in standard, Pro and Max versions with 10, 14 and 16 CPU cores, respectively. Apple earlier launched a chip called the M2 Ultra that combines two 2022 M-series processors into a single product.

The company is expected to take a similar approach with the upcoming M5 chip by offering it in standard, Pro, Max and Ultra editions. It’s unclear how many CPU cores the different versions will offer. However, Kuo detailed that all four processors are set to be made using a new version of TSMC’s three-nanometer node.

The chipmaker’s three-nanometer technology is currently in its second iteration. This second-generation process, which is known as N3E, offers 18% better performance or 32% lower power usage than the original. Apple’s M5 chips will reportedly be made using a newer version of the technology called N3P that will offer 5% higher performance than N3E or 10% lower power usage.

Cutting-edge processors have up to several hundred layers. N3P reduces some of the layers that must be made with EUV machines, the most complex lithography systems on the market, which will lower manufacturing costs. The technology also avoids the need for double patterning, a practice whereby some transistors are etched in two passes rather than one.

Apple’s M-series chips have until now featured a monolithic design, which means the CPU, GPU and AI accelerator are implemented on a single piece of silicon. The company is expected to take a different approach with the Pro, Max and Ultra versions of the M5. According to today’s report, Apple intends to implement the CPU and GPU as separate silicon dies that will be linked together into a single chip after manufacturing.

Production a chip’s compute modules separately helps cut costs. If one of the modules contains a manufacturing fault, the others can still be used, which reduces the need to discard the entire processor and thereby avoids the associated expense.

Apple will reportedly assemble the high-end M5 chips using 2.5D packaging. This is a chip design approach that places a processor’s compute modules atop a common base layer, or interposer. The interposer is itself a semiconductor that allows data to move between the chip’s other components.

Apple reportedly plans to implement the M5 series’ 2.5D packaging using a TSMC technology called SOIC. With SOIC, a chip’s compute modules are linked together by copper structures that are significantly smaller than earlier interconnects. This means more such copper structures can be included in the chip, which increases the rate at which data moves between its compute modules.

Apple is expected to debut the entry-level M5 in the first half of 2025. Devices powered by the Pro and Max editions are set to follow suit in the latter half of the year, while the M5 Ultra will reportedly launch in 2026.

Apple is expected to incorporate the chips into not only its Mac lineup but also its Private Cloud Compute, or PCC, servers. Those machines help power Apple Intelligence, a suite of AI features that recently started rolling out for iPhones.

Image: Apple

Your vote of support is important to us and it helps us keep the content FREE.

One click below supports our mission to provide free, deep, and relevant content.

Join our community on YouTube

Join the community that includes more than 15,000 #CubeAlumni experts, including Amazon.com CEO Andy Jassy, Dell Technologies founder and CEO Michael Dell, Intel CEO Pat Gelsinger, and many more luminaries and experts.

THANK YOU

Leave a Comment